# CPU Consumption, from Real-Time Embedded Systems to Mobile Devices

#### Dana VÎLCU

Spiru Haret University

Faculty of Mathematics and Informatics

d.vilcu.mi@spiruharet.ro

# CPU Consumption, from Real-Time Embedded Systems to Mobile Devices

- 1. Optimal task scheduling

- 2. Task scheduling and minimal CPU consumption

- 3. Computing hardware of mobile devices

Conclusion

## 1. Optimal task scheduling

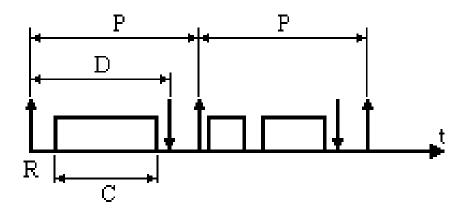

Task – duration, cost, activation, deadline, period

Feasable scheduling, optimal scheduling, optimal scheduler

[DER 74] *EDF — UP optimal for premptible and independent tasks* [MOK 83] *EDF — non MP optimal*

[MOK 83] Impossibility of optimal on-line scheduler for tasks with mutual exclusion constraints

## 1. Optimal task scheduling

[DER 89] – necessar and sufficient conditions for UP scheduling

- feasibility of periodical, independent tasks,

with same deadline and period

[DER 89] insufficient knowledge problem for optimal MP scheduling for tasks based on deadlines (without apriori complete knowledge on task duration, deadline and activation)

[DER 89] — conditions for feasible MP scheduling of independent tasks

## 1. Optimal task scheduling

[MNA 59] – for some metric, MP scheduling based on a finite number of preemptions is better than non-preemption

[GAR 75] – difficulty of non-preemptive MP scheduling for different models of tasks with the same deadline

[LAW 83] – MP preemptive scheduling with minimal delayed task is NP-hard

[GRA 76] – for a feasible model of tasks, changing initial conditions can give worst time of scheduling

Theoretical studies based on statistical analysis of the task parameters.

#### 2. Task scheduling and CPU consumption—theory

[CHA 92], [BRO 95], [BRE 95], [CHA 96], [TIW 98] — minimizing the power consumption by minimizing the voltage

- => technological evolution

- => not possible on-line

[MAL 94] - Intel DX2-486, 40Mhz

[LEE 96] - DSP Fujitsu CMOS, 40Mhz

[HON 99] - aproximation of the power consumption as a polynomial function of the CPU speed

=> at the same number of CPU cycles, the power consumption is dependent on the instructions used

CAMAI2013

# 2. Task scheduling and minimal CPU consumption

$g(S) = S^p, p \ge 2, p \in \mathbb{R}$  [YAO 95] <u>periodical independent tasks</u>

$$g(S) = \sum_{j=1}^{r} a_j S^j, r \in \mathbb{N}, r \ge 2, a_j \in \mathbb{R}, \forall j = 1,...,r$$

[AYD 01]

$$\left(\min \sum_{i=1}^{j=1} \sum_{j=1}^{P/P_i} E_i \left(S_{ij}\right)\right) \tag{1}$$

$$\left\{ \sum_{i=1}^{n} \sum_{j=1}^{P/P_i} \frac{C_i}{S_{ij}} \le P \right. \tag{2}$$

$$\begin{vmatrix}

S_{\min} \leq S_{ij} \leq S_{\max} & i = 1, ..., n & j = 1, ..., \frac{P}{P_i} \\

\text{feasible scheduling with } \left\{S_{ij}\right\}$$

(3)

feasible scheduling with

$$\{S_{ij}\}$$

(4)

[AYD 01] - UP static solution - same speed - maximal CPU capacity

- UP dynamic solution — on-line speed adjustment

[VIL04] - EDF optimal for power consumption

- general formula for tasks speed

# 2. Task scheduling and minimal CPU consumption periodical independent tasks

[VIL04] - generalisation for MP with variable speed

- necessar and sufficient condition for the feasibility

$$\max_{i=1,\ldots,n} \left( \overline{C}_i / D_i \right) \leq S_{MAX}$$

- task migration not efficient

- existence of a global optimal scheduling

- uniformity principle

- minimizing the power consumption by augmenting the number of the processors

$$\frac{1}{2^{r-1}}E_1 \le E_2 \le \frac{1+2^r}{3^r}E_1$$

- algorithm for evaluating the power consumption for a set of periodical independent tasks

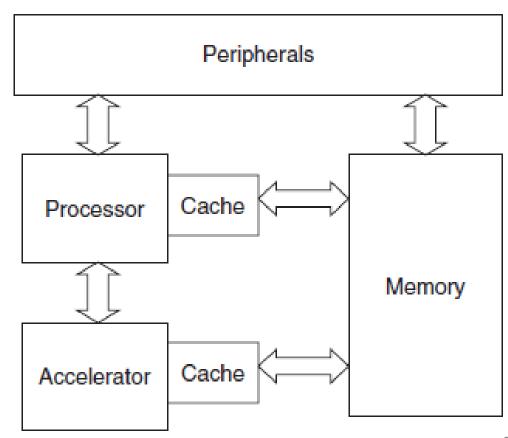

#### 3. Computing hardware of mobile devices

[CHA02] - typical signal processing task on a RISC machine (StrongARM, ARM9E) requires three times as many cycles as a C55x DSP while consuming more than twice the power

Integrating all of the subsystems into one chip

#### 3. Computing hardware of mobile devices

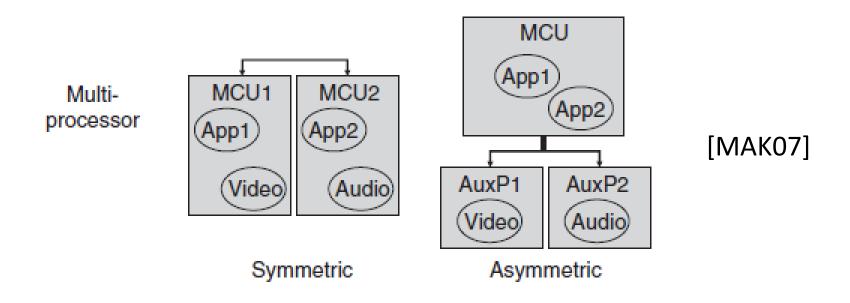

#### Symmetric multiprocessing (SMP)

- => balance load between each other [VILO4] energy saving

- => save energy by shutting down some of them when the load is low

- multiprocessing can be a relatively complex solution [VILO4] not necessary task migration

- processor-level granularity as basis of energy management?? [MAK07]

- [VIL04] theoretical important energy gain for same type of tasks

- [TEG11] experimental proof for energy gain

#### Asymmetric multiprocessing

- multiple specialized pieces of hardware

- eased design

- allocating tasks to different pieces of equipment

#### **Conclusion: Combining the two approaches**

CAMAI2013 10

#### 3. Computing hardware of mobile devices

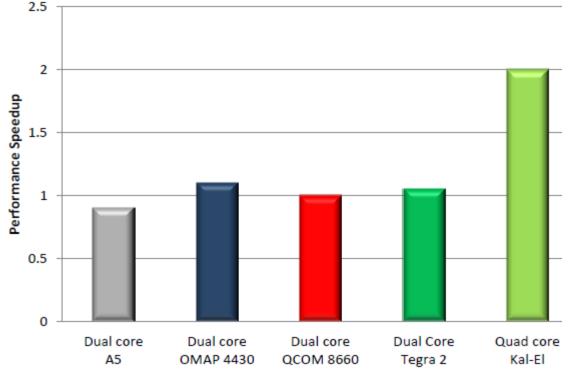

[TEG11] - beginning of 2011: multi-core CPUs (Tegra 2 – nVIDIA) - tablets and smartphones;

NVIDIA's Project Kal-El – vSMP – fifth CPU core (ARM Cortex A9) individually enabled and disabled based on the work load

=> lower power consumption, higher performance per Watt than

[TEG11] CoreMark Benchmark

Results

dual-core

CAMAI2013

#### Bibliography

- [MNA 59] R. McNaughton, Scheduling With Deadlines and Loss Functions, Manag. Sc., 6, p. 1-12

- [DER 74] M. Dertouzos, *Control Robotics: the procedural control of physical processors*, Proc. IFIP Congress, p. 807-813

- [GAR 75] M. R. Garey, D. S. Johnson, *Complexity results for multiprocessor scheduling under resource constraints*, SIAM Journal of Computing

- [GRA 76] R. Graham, Bounds on the Performance of Scheduling Algorithms, in Computer and Job Shop Scheduling Theory, John Willey and Sons, p. 165-227

- [LAW 83] E. L. Lawler, *Recent Results in the Theory of Machine Scheduling*, Mathematical Programming: the State of the Art, A. Bachen et al. (eds.), Springer Verlag, New York

- [MOK 83] A. K. Mok, Fundamental Design Problems for the Hard Real-Time Environments, MIT Ph.D. Th.

- [DER 89] M. L. Dertouzos, A. K. Mok, *Multiprocessor On-Line Scheduling of Hard-Real-Time Tasks*, IEEE Trans. on Soft. Eng., Vol. 15, No. 12

- [CHA 92] A. P. Chandrakasan et al., Low-Power CMOS Digital Design, IEEE J. Solid-State Circuits, Vol. 27, No. 4, pp. 473-484

- [MAL 94] S. Malik et al., *Power Analysis of Embedded Software: A First Step Towards Power Minimization*, Intl. Conf. on Computer Aided Design, San Jose, California

- [BRE 95] E. Brewer et al., *Design of Wireless Portable Systems*, Proc. IEEE Intl. Comp. Soc. Conf., pp. 169-176

#### Bibliography

- [BRO 95] R. W. Brodersen, A. Chandrakasan, *Minimizing Power Consumption in Digital CMOS Circuits*, Proc. IEEE, Vol. 83, No. 4, pp. 498-523,

- [YAO 95] F. Yao et al., A Scheduling Model for Reduced CPU Energy, Proc. 36th Annual IEEE Symp. Found. Comp. Sc.

- [CHA 96] A. P. Chandrakasan, et al., *Data Driven Signal Processing: An Approach for Energy Efficient Computing*, Proc. Intl. Symp. Low-Power Electronics and Design, pp. 347-352

- [LEE 96] M. T-C. Lee et al., Power Analysis and Minimization Techniques for Embedded DSP Software, IEEE Trans. VLSI Systems

- [HON 99] I. Hong et al., *Power Optimization of Variable-Voltage Core-Based Systems*, IEEE Trans. CAD of Integrated Circuits and Syst., Vol. 18, No. 12

- [AYD 01] serie of articles, ex. H. Aydin et al., *Determining Optimal Processor Speeds for Periodic Real-Time Tasks with Different Power Characteristics*, Euromicro Conf. Real-Time Syst. 2001

- [VIL 04] D. Vilcu, Systèmes temps réel embarqués: ordonnancement optimal de tâches pour la consommation énergétique du processeur, PhD Thesis, http://doxa.scd.univ-paris12.fr/theses/th0211370.pdf

- [MAK 07] T. Mikkonen, Programming Mobile Devices. An Introduction for Practitioners, Wiley, 2007

- [TEG 11] nVIDIA Whitepapers: Benefit of Multiple CPU cores in Mobile Devices, The Benefits of Quad Core CPUs in Mobile Devices

CAMAI2013